Sistemas

de memoria:

En

esta práctica del tema 5 hemos estudiado a fondo las memorias que

componen un pc, sus características y su funcionamiento. Para

realizar esta práctica hemos hecho uso del programa LogiSim.

Existen

varios tipos de memorias, cada una de ella responden a unas

necesidades específicas para cada situación, pero por norma

general, todas las memorias tienen en común que existen dos

características inversamente proporcionales, la velocidad y la

capacidad, de modo que cuando una sube la otra baja y viceversa.

La

capacidad y la velocidad son inversamente proporcionales

principalmente por temas de costes, cuando se consigue una tecnología

que logra una gran velocidad de transferencia de datos, su coste

suele ser muy alto, por lo que se reduce su capacidad para abaratar

el coste del producto y viceversa.

Hay

dos tipos de memorias, SRAM y DRAM, la principal diferencia entre

ambas es que la DRAM necesita refresco y la SRAM no y que la SRAM

está compuesta por biestables y la DRAM por condensadores. Debido a

estas composiciones la SRAM tiene una gran velocidad pero implementar

los biestables es muy costoso, por lo que se utiliza para lugares

donde se necesiten pequeñas cantidades de memoria como en las

caches, mientras que la DRAM tiene una velocidad más limitada al

estar compuesta por condensadores pero es muy fácil de hacer que

tenga una gran capacidad, por lo que se utiliza como memoria

principal. Otras características a tener en cuenta de las memorias

son la latencia, que no es más que el tiempo que tarda desde que se

le solicita un dato hasta que lo tiene en las patillas de salida, la

velocidad de transferencia, que es la velocidad en que transmite los

datos y se mide en bytes/s y tiempo de ciclo, que no es más que el

tiempo que pasa entre un ciclo y otro en las memorias DRAM. Al ser la

DRAM la que se usa como memoria principal, será en este tipo en la

que nos centremos de ahora en adelante.

Las

memorias DRAM se organizan por módulos y los módulos a su vez

contienen a uno o más chips de memoria trabajando en paralelo entre

ellos, para una mejor comprensión se aporta una imagen del esquema

típico de un módulo:

Pues

bien, tal y como puede verse en la imagen, el modulo aloja 8 chips

funcionando en paralelo, por lo que si cada chip es capaz de

almacenar una palabra de 8 bits, los 8 chips juntos devolverán al

bus de datos 64 bits.

Dentro

de las memorias DRAM existen variantes, que se han ido desarrollando

a lo largo del tiempo para mejorar sus características,

recientemente han estado las SDRAM, que son memorias síncronas con

una señal de reloj y las DDR que consiguen dos accesos a memoria por

ciclo. Dentro de las DDR en los últimos años han pasado de las DDR

a secas, a la DDR2 y DDR3, todas ellas consiguiendo un aumento de

velocidad de transferencia a la vez que bajando el consumo de

energía.

Las

memorias DRAM tienen al tener una gran capacidad se ha diseñado un

sistema llamado mapa de memorias con el que se sabe cuántos bits

serán necesarios para direccionar toda la memoria disponible de

forma que si se dispone de un bus de direcciones de 32 bits se podrán

direccionar 232

bits, lo que son 4GB y también es necesario indicar para que se

usara cada bit, para ello es importante tener en cuenta los

siguientes datos ordenado de bits menos significativos a más:

- Bits necesarios para identificar el byte. Ejemplo: Si el bus de datos es de 32 bits, pues 32/8=4 y 4=22 por lo que serán necesarios 2 bits para identificar la palabra que serán los bits A0 y A1.

- Numero de bits necesario para transportar la capacidad del módulo. Ejemplo: Si tiene una capacidad de 1 GB, podrá almacenar 128Mpalabras, por lo que 128=27 y 1024=220 siendo por tanto necesarios 27 bits, de A2-A29.

- Por último, si se tienen 2 módulos se necesitara identificar a que módulo ir. Ejemplo: serán necesarios 2=21 por lo que serán necesario un último bit A30.

- El último bit disponible que sobra, quedara libre y se indicara asi en el mapa de memorias.

Tras

lo dicho hasta ahora es suficiente para tener una buena idea de cómo

son y funcionan las memorias DRAM, pero ahora si solo se dispusiera

de este tipo de memorias en un PC cuando la CPU necesite algún dato

debería de acceder directamente a la memoria principal, pero tal

como se ha explicado anteriormente las memorias DRAM son lentas en

comparación con otros componentes, como por ejemplo la CPU, por lo

que se produciría un cuello de botella, para evitar este problema se

creó lo que se conoce como memoria cache.

Las

memorias cache no son más que memorias hechas con memoria SRAM y que

por lo tanto son increíblemente rápidas pero de pequeña capacidad.

Los datos más usados por la CPU son enviados a la cache, por lo que

la CPU tratara de funcionar siempre que pueda con esta memoria, de

forma que, cuando la CPU solicita un dato lo busca primero en la

memoria cache y si no lo encuentra lo busca en la memoria principal

con el consiguiente aumento de tiempo que esto supone, por lo que la

primera opción siempre es la memoria cache.

A

continuación explicaremos los ejercicios realizados durante las

prácticas.

Primero

diremos qué son: S, L, CLOCK y CLEAR.

S:

Selección, si no se activa el seleccionador nada de lo que ocurra en

el módulo quedara almacenado.

CLOCK:

La señal de reloj, recoge los datos en el flanco de subida.

L:

Load, cuando está activo es cuando saca los datos hacia el bus de

datos.

CLEAR:

Cuando se activa se resetean todos los valores de la memoria RAM.

Ejercicio

1:

Introducir

una memoria RAM de 64Kx8 y realizar un circuito que permita leer y

escribir en ella. Probar a introducir en las direcciones 0023h el

dato 3A y en la dirección C120h el dato 25.

Lo

primero a analizar aquí es que significa 64Kx8, con 64K habla de la

capacidad de la memoria y con 8 especifica que salida que tendrá al

bus de datos.

Para

hacer el ejercicio introducimos el valor en binario de 0023h

y 3A en entrada, activamos el triestado, S y CLOCK y se queda

registrado en la memoria RAM.

Ya

está almacenado el dato 3A en memoria, para la dirección C120h

y el dato 25, sería hacer exactamente lo mismo solo que cambiando la

dirección y la entrada por los datos ahora facilitados.

Ejercicio

2:

Unir

dos memorias del tipo utilizado en el apartado 1, para conformar una

de 64Kx16. Comprobar su funcionamiento de forma similar al apartado

anterior: introduciendo algunos datos de 16 bits en varias

direcciones.

Construimos

el circuito en Logisim:

Para

probar su funcionamiento indicamos una dirección y añadimos un

valor en la entrada de datos.

Por

último sólo nos queda seleccionar en memoria la dirección que

hemos indicado y cargar el dato en esa dirección.

Como

podemos ver en la imagen, ya hemos cargado en memoria el dato.

Primero,

activamos SEL para poder posicionarnos en memoria según la dirección

que indicamos.

Segundo,

activamos el triestado de entrada de datos para que llegue al bus y

finalmente activamos E para cargar el dato en la memoria.

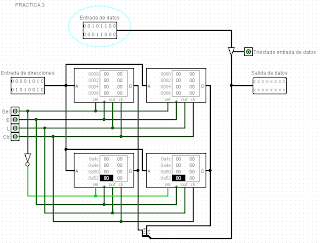

Ejercicio

3:

Unir

tres memorias para como las de los apartados anteriores (64Kx8) para

conformar una de 128Kx16. Comprobar su funcionamiento de forma

similar al apartado anterior: introduciendo algunos datos de 16 bits

en varias direcciones.

Construimos

el circuito en Logisim:

En

este ejercicio tendremos la opción de elegir la pareja de memorias

de arriba o la de abajo, esto se hace mediante el inversor que hay en

el selector, por tanto una pareja estará seleccionada y la otra no.

Esto podemos verlo claramente en la imagen.

Pues

bien, vamos a probar nuestro circuito. Como en los ejercicios

anteriores, primero indicamos la dirección de memoria en la cual

queremos guardar el dato. En entrada de datos indicaremos el dato que

queremos guardar en la dirección que indicamos anteriormente.

Podemos

ver que antes teníamos seleccionada la pareja de memoria de abajo y,

al activar SEL, hemos activado las memorias de la parte superior de

la imagen.

Para

terminar el ejercicio, desactivo SEL y vuelvo a seleccionar las

memorias de la parte inferior de la imagen. Ahora que estamos

situados en la dirección que indicamos para guardar el dato en

memoria, activamos el triestado de entrada de datos y tenemos en el

bus el dato que queremos guardar. Finalmente activamos E y se guarda

en memoria el dato que queríamos para la dirección que hemos

indicado.

Ejercicio

4:

Ampliar

la memoria hasta 256Kx16 ¿Qué elemento será necesario para

seleccionar cada banco de dos memorias de 64Kx8? Un decodificador.

Comprobar su funcionamiento de forma similar al apartado anterior:

introduciendo algunos datos de 16 bits en varias direcciones.

Implementamos

el circuito en logisim:

A

continuación, procederemos a probar el circuito implementado, lo

primero que deberemos hacer es indicar la dirección de memoria en la

que queremos guardar el dato, la indicaremos en la entrada de

direcciones. Una vez realizada dicha operación procederemos a

introducir el dato, en la entrada de datos que posteriormente

guardaremos en la dirección de memoria antes introducida.

Una

vez tengamos introducidas la dirección de memoria, y el dato que

queremos introducir, procederemos a seleccionar el modulo mediante el

selector, en este caso vamos a seleccionar el modulo 1, para ello

solo tenemos que indicarlo en el selector con el codigo (“01”).

El

siguiente paso, será abrir el triestado de entrada de datos para

permitir el paso del dato antes introducido al bus interno, y por

ultimo le damos carga E y almacenaríamos el dato en la dirección de

memoria que hayamos introducido.

Ejercicio

5:

Transformar la estructura del

anterior punto para que los primeros 64K sean de memoria ROM Observar

que señales de control son las que intervienen en cada tipo de

memoria. Indica en cada bando la el banco de direcciones de memoria

que direcciona y obtén el mapa de memoria del conjunto.

Lo

primero sería implementar el circuito en logisim:

Por ultimo, realizamos el mapa de memoria que se muestra a continuación, donde aparece el rango de direcciones y los componentes que componen el circuito.

Direcciones

|

Componente

|

0 – 65535

|

MODULO ROM

|

65536 – 131071

|

MODULO RAM 1

|

131072 – 196607

|

MODULO RAM 2

|

196608 – 262143

|

MODULO RAM 3

|

No hay comentarios:

Publicar un comentario